1.1.CPU

简介

计算机的工作过程就是计算机执行程序的过程。程序是一个指令序列,这个序列明确告诉计算机应该执行什么操作,在什么地方能够找到用来操作的数据。

一旦把程序装入主存储器,计算机就可以自动执行取出指令和执行指令的任务。专门用来完成此项工作的计算机部件称为中央处理器(Central Processing Unit, CPU),做成单片集成电路的CPU通常又称为微处理器(Microprocessor),在一个集成电路中集成了两个 CPU 芯片,称之为双核(dual core)微处理器。现代的个人计算机一般都是使用微处理器作为CPU。

注意:CPU不是指一个特定的某一类东西,而是具有某种功能的部件的总称。 所以,不管是何种形态、设计、原理的部件,只要它能具有取出指令、执行指令的功能,它就是CPU。 简而言之,CPU 是用来表示计算机内部元件功能的术语。

顶视图是CPU的顶盖,用来保护CPU Die。底视图是CPU引脚,引脚用于输入或输出电信号,CPU通过引脚控制整个计算机。

计算机工业从1960W年代早期开始使用CPU这个术语。迄今为止,CPU从形态、设计到实现都已发生了巨大的变化,但是其基本工作原理却一直没有大的变化。

早期的CPU通常是为大型、特定的应用而定制的。目前,这种为特定应用而设计定制CPU的昂贵方法,在很大程度上已经让位于可大规模生产的通用处理器。这种标准化趋势,诞生于分立晶体管大型计算机(Mainframe)和小型计算机(Minicomputer)年代,并且随着集成电路(IC)的普及而大大加速。

现代的CPU使用集成电路制作,集成电路可以把日益复杂的CPU设计制造在很小的空间里。CPU的小型化和标准化,大大增加了这些数字器件在现代生活中的应用范围,远远超出了专用运算机器这一有限的应用。现代微处理器已经随处可见,从汽车到手机,甚至儿童玩具。

CPU工作过程

CPU和内存由数字集成电路(数字芯片)构成,集成电路通常称为IC(Integrated Circuit),它由晶体管组成,每一个晶体管具有ON/OFF两个状态。CPU中不同的数字电路实现不同的运算,相同的运算也可以用不同的数字电路实现。CPU能实现的各种最基本的运算统称为指令集,而 CPU自身就是一种指令集的实现。

实际上,从计算机组成的层次结构看,计算机指令又分为微指令、机器指令、宏指令。

微指令:微程序级的命令,属于硬件。

宏指令:若干条机器指令组成的命令,属于软件(汇编语言的宏指令)。

机器指令:通常所说的指令,介于微指令和宏指令之前 ,可完成一个独立的算术运算或逻辑运算操作。机器指令是CPU可以直接识别(执行)的指令。

CPU的基本工作是执行内存中的指令序列,即程序。

几乎所有的冯诺伊曼型计算机的CPU,其工作都可以分为5个阶段:取指令、指令译码、执行指令、访存取数和结果写回。其中取指令、指令译码、执行指令是三个不可或缺的阶段。

计算机在工作时,CPU会不断重复这5个过程,除非遇到停机指令。

1.取指令

取指令(Instruction Fetch,IF)是将一条指令从主存中取到指令寄存器的过程。指令先从内存中被取到数据缓冲寄存器(DR),然后送入指令寄存器(IR)。

2.指令译码

取出指令后,计算机立即进入指令译码(Instruction Decode,ID)阶段。

在指令译码阶段,指令译码器(ID)按照预定的指令格式,对指令寄存器(IR)中的指令进行拆分和解释,识别和区分出不同的指令类别及各种获取操作数的方法。

在组合逻辑控制的计算机中,指令译码器对不同的指令操作码产生不同的控制电位,以形成不同的微操作序列;在微程序控制的计算机中,指令译码器用指令操作码找到执行该指令的微程序的入口,并从此入口开始执行。

在传统的设计里,CPU中负责指令译码的部分是无法改变的硬件。不过,在众多运用微程序控制技术的新型CPU中,微程序有时是可重写的,可以通过修改成品CPU来改变CPU的译码方式。

3.执行指令阶段

在取指令和指令译码阶段之后,接着进入执行指令(Execute,EX)阶段。

此阶段的任务是完成指令所规定的各种操作,具体实现指令的功能。为此,CPU的不同部分被连接起来,以执行所需的操作。

例如,如果要求完成一个加法运算,算术逻辑单元(ALU)将被连接到一组输入和一组输出,输入端提供需要相加的数值,而输出端将含有最后的运算结果。

4.访存取数阶段

根据指令需要,有可能要访问主存,读取操作数,这样就进入了访存取数(Memory,MEM)阶段。

此阶段的任务是:根据指令地址码,得到操作数在主存中的地址,并从主存中读取该操作数用于运算。

5.结果写回阶段

作为最后一个阶段,结果写回(Writeback,WB)阶段把执行指令阶段的运行结果数据“写回”到某种存储形式。结果数据经常被写到CPU的内部寄存器中,以便被后续的指令快速地存取。在有些情况下,结果数据也可被写入相对较慢、但较廉价且容量较大的主存。许多指令还会改变程序状态字寄存器中标志位的状态,这些标志位标识着不同的操作结果,可被用来影响程序的动作。

在指令执行完毕、结果数据写回之后,若无意外事件(如结果溢出等)发生,计算机就接着从程序计数器PC中取得下一条指令地址,开始新一轮的循环,下一个指令周期将正常地顺序取出下一条指令。

许多新型CPU可以同时取出、译码和执行多条指令,体现出并行处理的特性。

CPU部件

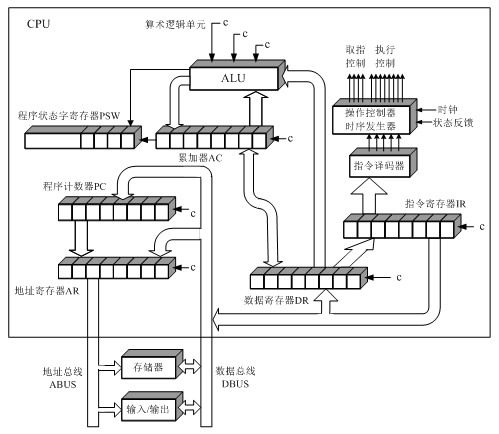

从功能方面来看,CPU的内部由寄存器、控制器、运算器和时钟四个部件构成,其中,控制器和运算器是CPU不可或缺的部件。各部件之间由电流信号相互连通。

-

寄存器用来暂存指令、数据等处理对象,是储存器的一种。根据种类的不同,一个 CPU 内部会有20~100个寄存器。

-

控制器负责把内存上的指令、数据等读入寄存器,并根据指令的执行结果来控制整个计算机。

-

运算器负责运算从内存读入寄存器的数据。

-

时钟负责发出 CPU 开始计时的时钟信号。不过,也有些计算机的时钟位于 CPU 的外部。

寄存器

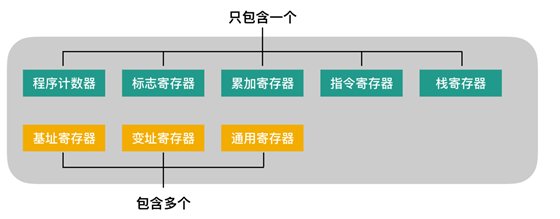

分为通用寄存器和专用寄存器。专用寄存器作用是固定的,如控制器和运算器中的寄存器。而通用寄存器可以由程序员指定用途。

根据功能的不同,可以将寄存器大致划分为八类。可以看出,寄存器中存储的内容既可以是指令也可以是数据。其中,数据分为“用于运算的数值”和“表示内存地址的数值”两种。 数据种类不同,存储该数值的寄存器也不同。CPU 中每个寄存器的功能都是不同的。

| 种类 | 功能 |

|---|---|

| 累加寄存器 accumulator | 存储执行运算的数据和运算后的数据 |

| 标志寄存器 flag register | 存储运算处理后的 CPU 的状态 |

| 程序计数器 program counter | 存储下一条指令所在内存的地址 |

| 基址寄存器 base register | 存储数据内存的起始地址 |

| 变址寄存器 index register | 存储基址寄存器的相对地址 |

| 通用寄存器 general purpose register | 存储任意数据 |

| 指令寄存器 instruction register | 存储指令。CPU 内部使用,程序员无法通过程序对该寄存器进行读写操作 |

| 栈寄存器 stack register | 存储栈区域的起始地址 |

其中程序计数器、累加寄存器、标志寄存器、指令寄存器和栈寄存器都只有一个,其他寄存器一般有多个。

寄存器对程序员来说比较特殊,因为在汇编语言中,程序员需要直接操纵寄存器:

# 汇编语言编写的程序示例

mov eax, dword ptr [ebp-8] # 把数值从内存复制到 eax

add eax, dword ptr [ebp-0Ch] # exa 的数值和内存的数值相加

mov dword ptr [ebp-4], eax # 把 exa 的数值(上一步的相加结果)存储在内存中

eax 和 ebp 是 CPU 内部的寄存器的名称。内存的存储场所通过地址编号来区分,而寄存器的种类则通过名字来区分。

运算器

- 算术逻辑单元(Arithmetic and Logic Unit,

ALU):负责对数据进行算术运算和逻辑运算。 - 累加寄存器(

AC):累加器,通用寄存器,为ALU提供了一个工作区。 - 数据缓冲寄存器(

DR):为CPU和内存、外围设备之间数据传送的中转站、缓冲。 - 状态条件寄存器(

PSW):包括状态标准和控制标志,例如进位(C)、溢出(V)、运算结果为0(Z)、运算结果为负值(N)、中断(I)等。

控制器

控制器用于控制整个CPU的工作。一般包括:

- 指令寄存器(

IR):当CPU执行一条指令时,先把它从内存中取到DR,然后送入IR暂存。指令译码器根据IR的内容产生各种微操作指令,控制其他部件完成工作。 - 程序计数器(

PC): 又称之为指令计数器,PC有寄存信息和计数两个功能。执行指令时,CPU将自动修改PC内容,使其保持的总是将要执行的下一条指令的地址。 - 地址寄存器(

AR): 保存了当前CPU所访问内容单元的地址,直到对内存的读写操作完成。 - 指令译码器(

ID): 指令分为操作码和地址码两部分。ID是对指令中的操作码字段进行分析解释,识别指令规定的操作,向操作控制器发出具体的控制信号,控制各部件完成工作。

其他还包括:

- 时序控制器:为每条指令按时间顺序提供有效的控制信号。

- 总线逻辑:信息通路的控制电路。

- 中断控制器:用于控制各种中断请求,并根据优先级进行排队,逐个交给CPU处理。

- e.t.c

流水线技术

CPU可以有分开的取值单元、解码单元、和执行单元。也就是说,不必等到一条指令从头到尾执行完毕后再开始处理下一条指令。三级流水线其示意图为:

// 流水线技术

^

| X : 取指流水线

| Y : 解码流水线

| Z : 执行流水线

|

|

+-------+ +------+------+-----------------+-----+

X | 1 | 2 | ... | n |

+-------+ +----------+------+-------------+----------+

Y | | 1 | | 2 | ... | n |

+-------+ | +------+---------+-----+-----+-+---------+

Z | | 1 | 2 | 3 | ... | | n | 时间

+-------+ +-----------------+-----+-----+-----+------------------>

|XXXXXX|YYY| |ZZZZ|

|XXXXXX|YYY| |ZZZZ|

+----------+ +----+

在某个时刻,第一条指令取指完成(对应图中XXXXXX标注区域),解码流水线立即开始第一条指令的解码,同时取指流水线开始对第二条指令的取指;第一条指令的解码操作完成之后(对应图中YYYY标注区域),执行流水线开始对第一条指令的执行操作,同时解码流水线等待第二条指令送达。